���]ϵ�y(t��ng)���d��� ����Windows10ϵ�y(t��ng)���d ����Windows7ϵ�y(t��ng)���d xpϵ�y(t��ng)���d ��X��˾W(w��ng)indows7 64λ�b�C�f�ܰ����d

��QuartusII15���d��Quartus II 15.0���d(��ע�ԙC) �e��

- ܛ����ͣ��ИI(y��)ܛ��

- ܛ���Z�ԣ����w����

- �ڙ�(qu��n)��ʽ�����Mܛ��

- ���r�g��2024-12-08

- ��x��(sh��)����

- ���]�Ǽ�:

- �\�Эh(hu��n)����WinXP,Win7,Win10,Win11

ܛ����B

Quartus II 15.0�e����һ��dz����õķdz����õ�programmable logic device��Field Programmable Gate ArrayоƬ���_�l(f��)ܛ����ܛ��15.0�汾�ѽ�(j��ng)���������M���˃�(y��u)�������OӋ���и��õ�Ч�ʣ���ԭ���������������M���˸��£������������Ñ���ܛ��Ҳ��һ���Ľ̳̣���ʹ���ϸ��ӱ�ݡ�

Quartus II 15.0�e����Altera��˾�_�l(f��)�ģ�ܛ���������µ��㷨��������TimeQuest�r������������ٶ��ϵ��������ஔ���Ñ��Ĺ���Ч�ʵ�������Quartus II 15.0�e��F(xi��n)�ڌ���������U���˺ܶ����M��IP���������T�������е�ˮƽ��С��邃���f��ķdz��Ѻ�~

ܛ�����c

1��������ԭ��D���Y(ji��)��(g��u)��D��VerilogHDL��AHDL��VHDL����·�����������䱣����OӋ���w�ļ�;

2��оƬ(�·)ƽ�沼���B����;

3��LogicLock�����OӋ�������Ñ��ɽ�������(y��u)��ϵ�y(t��ng)��Ȼ�����ӌ�ԭʼϵ�y(t��ng)������Ӱ��^С��oӰ푵ĺ��m(x��)ģ�K;

4���������߉�C�Ϲ���;

5�������·���ܷ����c�r��߉���湤��;���r/�r������c�P�I·���ӕr����;��ʹ��SignalTap II߉���������M��Ƕ��ʽ��߉����;

6��֧��ܛ��Դ�ļ������Ӻ̈́�(chu��ng)������������朽��������ɾ����ļ�;

7��ʹ�ýM�Ͼ��g��ʽ��һ��������w�OӋ����;

8���ԄӶ�λ���g�e�`;

9���������g�����c��C����;

10�����x��˜ʵ�EDIF�W(w��ng)���ļ���VHDL�W(w��ng)���ļ���Verilog�W(w��ng)���ļ�;

11�������ɵ�����EDAܛ��ʹ�õ�VHDL�W(w��ng)���ļ���Verilog�W(w��ng)���ļ���

Quartus II 15.0�e���e�̳�

һ�����b��횽M��

1��QuartusSetup-15.0.0.145-windows.exe

2��QuartusHelpSetup-15.0.0.145-windows.exe

ע���b��Ҫ���ӣ������Ć��ӽ���r���x“Cancel”

��������

1���≺�_license.zip

2���\�������“QuartusCrack.exe”

3���c�����ң��x��"C:\altera\15.0\quartus\bin64\gcl_afcq.dll"

4���c����һ��

5���c�����

6������ “Quartus II 15.0 (64-bit)”(���w��·����C:\altera\15.0\quartus\bin64\quartus.exe)

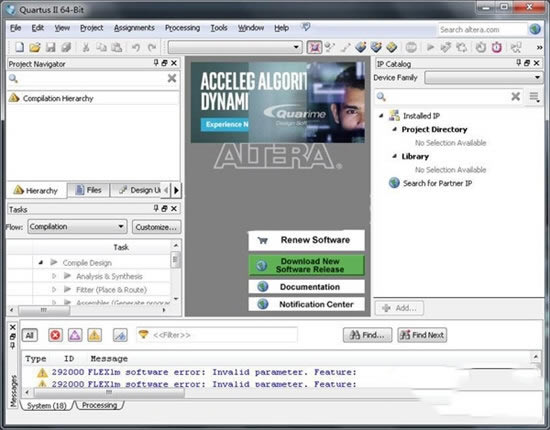

7����“Evaluation Mode”�����x��“if you hava a valid license file, specify the location of your license file”���c�� ok

8���@ȡNIC ID�����ҵ��ǣ�a088699e34fa , a088699e34fe , 00155d007301

9�����≺�_��“license.dat”��ؐһ�ݵ� "C:\altera\15.0\licenses\license.dat"�� �����е���̎ XXXXXXXXXXXX ���Լ��� NIC ID��(ע���ʽ�����ҵ��� "a088699e34fa a088699e34fe 00155d007301"��������̖�����g�ÿո�ָ�)

10���x�� “C:\altera\15.0\licenses\license.dat”���c�� OK

�������b������

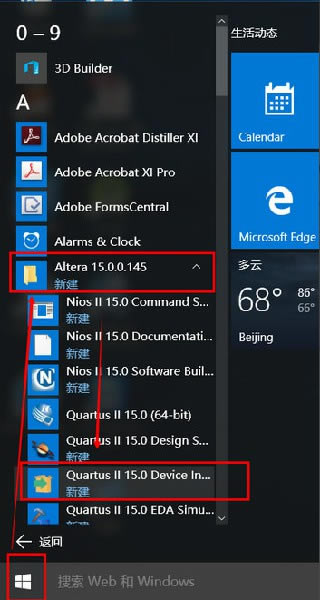

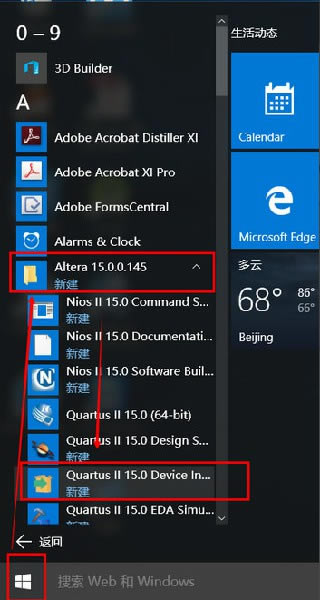

1���\��"ϵ�y(t��ng)�_�l(f��)�ˆ�"->���Б���->Altera 15.0.0.145->Quartus II 15.0 Device Installer

2���x�����d�����������ڵ�Ŀ䛣��c�� next;

3���x�����еď��x���c��next���_ʼ�˰��b

�ġ����b�Uչ��

���ڔUչ����Ҫ�� exe �Ɉ�(zh��)�г��������b����Ҳ���^�ĺ���

�塢�x�b�M��-�Uչ�������bһЩ�Uչ���ܰ��x�b�M��

1��DSP Builder(��MATLAB�IJ�������Բ��b����Ҫ������̖̎��a(ch��n)Ʒ�_�l(f��))57MB DSPBuilderSetup-15.0.0.145-windows.exe

2��SOC(����b�����_�l(f��)���ɸ�����Ӳ��Cortex-A��SOC FPGA����(n��i)��ȫ���������ARM�_�l(f��)���ߣ�����ARM��˾��DS-5���b��)2.2GB SoCEDSSetup-15.0.0.145-windows.exe

3��JNEye(���Բ��b������FPGA�����հl(f��)����PCB���ķ���ͷ���������FPGA�ĸ����հl(f��)�����Ͳ��ð��b�@������)1.1GB JNEyeSetup-15.0.0.145-windows.exe

4��Altera OpenCL(��C�Z���_�l(f��)FPGA�Ĺ��ߣ����Բ��b����Ҫ������̖̎���ͿƌWӋ��a(ch��n)Ʒ�_�l(f��))

�� Altera SDK for OpenCL 192MB AOCLSetup-15.0.0.145-windows.exe

�� Altera Runtime Environment for OpenCL Linux x86-64 RPM 612KB aocl-rte-15.0.0-1.x86_64.rpm

�� Altera Runtime Environment for OpenCL Linux PowerPC RPM 480KB aocl-rte-15.0.0-1.ppc64.rpm

�� Altera Runtime Environment for OpenCL Linux Cyclone V SoC TGZ 706KB aocl-rte-15.0.0-1.arm32.tgz

�� Altera Runtime Environment for OpenCL Windows x86-64 8.9MB aocl-rte-15.0.0.145-windows.exe

5��ModelSim AE(���Բ��bAE�棬���]���õ�ModelSim SE�棬��ȥMentor�ٷ��W(w��ng)վ���dܛ��������SE�汾10.3d��ȥeetopՓ�����dCrack��SE���e��Ҳ��������AE��)1.1GB ModelSimSetup-15.0.0.145-windows.exe

6��Quartus II Programmer(���h���S������ˮ���ϰ��b����ͨ�_�l(f��)�߲�Ҫ���b�����Quartus II�ѽ�(j��ng)�����˴˹���) 607MB QuartusProgrammerSetup-15.0.0.145-windows.exe

�������������d��ַ

����ȫ�b�����Ă�ϵ�е������Ͱ��b�Ă�ϵ�е������죬ֱ�ӏ����B�ӵ�Ѹ���м������d�������ܛ����С�ǽo����������ģ����Ï���

Arria II

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/arria-15.0.0.145.qdz 665MB

Arria 10

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/arria10_part1-15.0.0.145.qdz 2.7GB

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/arria10_part2-15.0.0.145.qdz 3.4GB

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/arria10_part3-15.0.0.145.qdz 2.7GB

Arria V

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/arriav-15.0.0.145.qdz 1.3GB

Arria V GZ

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/arriavgz-15.0.0.145.qdz 1.9GB

Cyclone IV

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/cyclone-15.0.0.145.qdz 464MB

Cyclone V

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/cyclonev-15.0.0.145.qdz 1.1GB

MAX II,MAX V

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/max-15.0.0.145.qdz 11.3MB

MAX 10

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/max10-15.0.0.145.qdz 295MB

Stratix IV

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/stratixiv-15.0.0.145.qdz 535MB

Stratix V

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/stratixv-15.0.0.145.qdz 2.8GB

DSP Builder(��MATLAB�IJ�������Բ��b����Ҫ������̖̎��a(ch��n)Ʒ�_�l(f��))

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/DSPBuilderSetup-15.0.0.145-windows.exe 57MB

SOC(����b�����_�l(f��)���ɸ�����Ӳ��Cortex-A��SOC FPGA����(n��i)��ȫ���������ARM�_�l(f��)���ߣ�����ARM��˾��DS-5���b��)

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/SoCEDSSetup-15.0.0.145-windows.exe 2.2GB

JNEye(���Բ��b������FPGA�����հl(f��)����PCB���ķ���ͷ���������FPGA�ĸ����հl(f��)�����Ͳ��ð��b�@������)

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/JNEyeSetup-15.0.0.145-windows.exe 1.1GB

Altera OpenCL(��C�Z���_�l(f��)FPGA�Ĺ��ߣ����Բ��b����Ҫ������̖̎���ͿƌWӋ��a(ch��n)Ʒ�_�l(f��))

Altera SDK for OpenCL

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/AOCLSetup-15.0.0.145-windows.exe 192MB

Altera Runtime Environment for OpenCL Linux x86-64 RPM

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/aocl-rte-15.0.0-1.x86_64.rpm 612KB

Altera Runtime Environment for OpenCL Linux PowerPC RPM

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/aocl-rte-15.0.0-1.ppc64.rpm 480KB

Altera Runtime Environment for OpenCL Linux Cyclone V SoC TGZ

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/aocl-rte-15.0.0-1.arm32.tgz 706KB

Altera Runtime Environment for OpenCL Windows x86-64

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/aocl-rte-15.0.0.145-windows.exe 8.9MB

ModelSim AE(���Բ��bAE�棬���]���õ�ModelSim SE�棬��ȥMentor�ٷ��W(w��ng)վ���dܛ��������SE�汾��ȥeetopՓ�����dCrack��SE���e��Ҳ��������AE��)

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/ModelSimSetup-15.0.0.145-windows.exe 1.1GB

Quartus II Programmer(���h���S������ˮ���ϰ��b����ͨ�_�l(f��)�߲�Ҫ���b�����Quartus II�ѽ�(j��ng)�����˴˹���)

http://download.altera.com/akdlm/software/acdsinst/15.0/145/ib_installers/QuartusProgrammerSetup-15.0.0.145-windows.exe 607MB

������

1������ Spectra-Q ������������OӋЧ��

�˽����������Ӝp���OӋ�����;��g����׃�� FPGA �OӋЧ�ܵ�δ����

2������֪�R

�F(xi��n)�ڿ��� ���d �µı���֪�R���˽� Spectra-Q™ �����Ԕ����Ϣ���˽��������������OӋҎ(gu��)���͌�ʩ�������A���ṩ�˸���Ŀ��ƹ��ܺ��A�y���ܡ���߀���˽ Spectra-Q ���H�s���˾��g�r�g������߀�p�����OӋ�����Ŀ��Δ�(sh��)����˳ɹ��Ľ�Q���OӋЧ�܆��}��

3�����̵ľ��g�r�g

Spectra-Q �����������ԣ����g�r�g���OӋ�����ٶ������ 8 �������M�a(ch��n)Ʒ��Ѹ�����У�

·���î���Ķ�˹���վ���㷨�ٶȸ��� (�C�ϡ����֡��������r��������Լ������C��)

·�u�Mʽ����֧���OӋ�ˆT�����M�뾎�g�A�Σ���(y��u)�������OӋ���֣��@���s�����OӋ�����r�g

·�������¾��g��������ʹ���˾C�ϺͲ��ֲ�����Ϣ��������̎��С�ĝu�Mʽ�OӋ�ģ��A�C�� HDL �ĵľ��g�ٶ������ 3 �������m�� SignalTap® II ߉�������ĵľ��g�ٶ������4��

·�ֲ�ʽ���g֧�������OӋ�M�Є��֣��ڷ�����Ⱥ�Ķ��_Ӌ��C���M�в��о��g���O��Ŀs���˾��g���r�g

4�����ٵ��OӋ����

Spectra-Q ���������еĹ��ߺ��ܜp������� FPGA �� SoC �OӋ������OӋ�����Δ�(sh��)��

·BluePrint ƽ�_�OӋ�� — BluePrint ƽ�_�OӋ������ Spectra-Q �������̽���������O�wϵ�Y(ji��)��(g��u)����Ч�ķ���ӿڡ�BluePrint ���r�M���m���Լ��Ϸ��z�飬��ֹ�˷Ƿ����_���䣬�����ˏ��s���e�`��Ϣ��Ҳ����Ҫ�ȴ�ȫ���g��I/O �OӋ�ٶ������ 10 ����Ԕ���˽�·ʹ�� BluePrint ƽ�_�OӋ�� �������� I/O �OӋ��

·��ϲ����� — Spectra-Q ����߀֧�ֻ�ϲ��������ԣ�ʹ�������M�IJ����㷨����߉���w���֡���ϲ������Y(ji��)�Ϸ������˻��g������˽Y(ji��)���|(zh��)���������˷N�������Ķ������˕r���Ք���

5��������OӋݔ��

߀��Ӳ����ܛ���͔�(sh��)����̖̎�� (DSP) �OӋ�ˆT�ṩ�� Spectra-Q ������ٸ�ۙ�OӋݔ�빦�ܡ�ͨ�^�����OӋݔ�뷽�����OӋ�ˆT�����Լ�ϲ�g���OӋ�h(hu��n)��������Ч��ᘌ� FPGA �M���OӋ��

·���� C ���� C++ — Spectra-Q ����֧�֞���C���ṩ�� A++ �¾��g������ C ���� C++ �Z���н���֪�R�a(ch��n)��(qu��n) (IP) ��(n��i)�ˣ�ͨ�^���ٷ���� IP ���ɹ��ܴ���������Ч�ܡ�

·���� C (OpenCL) — ܛ���_�l(f��)�ˆT����ʹ����Ϥ�Ļ���C���OӋ���̺� ���� OpenCL �� Ӣ�ؠ�® SDK��SDK �ṩܛ������ģ�ͣ���������y(t��ng)�� FPGA Ӳ���OӋ���̡�

·����ģ�� — DSP Builder ���� ֧�ֻ���ģ�͵��OӋ���̣���ֱ���� Simulink ܛ���У������� DSP �㷨������ HDL��

·���� RTL — Quartus Prime ܛ��֧�����И˜��Z�ԣ����� SystemVerilog �� VHDL-2008��

6���� Stratix 10 FPGA �� SoC �ṩ Spectra-Q ����

Stratix 10 FPGA �� SoC ����һ�����Д�(sh��)���f߉��Ԫ (LE) �������� FPGA �OӋܛ����Ҫ�·�����Spectra-Q ����� Quartus Prime ܛ���ṩ֧�֣���� Stratix 10 ������ �OӋЧ�ܣ����M�a(ch��n)Ʒ���r���С�

Stratix 10 FPGA �� SoC Ӳ�����F(xi��n)�˄�(chu��ng)�£��e�����`���ģ�K���wϵ�Y(ji��)��(g��u)���M���������ķ��OӋ�����c Spectra-Q ����һ����(y��u)�����@�����Ч�ܵ��P�I��������

·�µ� HyperFlex ��(n��i)���wϵ�Y(ji��)��(g��u)����(li��n)�Y(ji��)��(g��u)�ϱ鲼�Ĵ��������ܱ�ǰ�״� FPGA ����� 2 ��

·�ɾ��̕r犘�C��

·���û����ȅ^(q��)�ķ����������M������

·Spectra-Q ����l(f��)�]�@�N�`���Ժ�ģ�K���ă�(y��u)�ݣ��O��Ĝp�����OӋ�����Δ�(sh��)���������OӋ���ã��������wϵ�Y(ji��)��(g��u)̽���Ҏ(gu��)����

7��ʹ��Spectra-QӲ�����M��IP������ʾ

Spectra-Q�����IP�����ṩ�ˏ�����¹��ܡ����磬F(xi��n)PGA���и���I/O�ӿڣ��ԘO�ߵĔ�(sh��)��(j��)������FPGA�ܘ�(g��u)���͔�(sh��)��(j��)�����I/O���ܘ�(g��u)���͕r���܉�ɹ����Ք�������Ϊ��Ĕ�(sh��)��(j��)��——“Ӳ����”�惦����ô�������ڿs�̮a(ch��n)Ʒ���Еr�g���@һ��(sh��)��(j��)�챣�ֲ�׃����FPGA�ܘ�(g��u)���OӋ�����������M�оC�ϡ����ֺͲ����Ķ����ӆ�������ҕ�l��ʾ��������Quartus Prime Pro��ܛ���������OӋӲ���ց�����������I/O���ܘ�(g��u)���ͣ�ԓ��ܛ������Spectra-Q����֧�ֵġ�

1�M���ƽ̌Wͨ2.0-�M���ƽ̌Wͨ2.0���d v5......

2step7 microwin-���T��PLC S7......

3�ٶȾW(w��ng)�P��ˬ����������-�W(w��ng)�P����-�ٶȾW(w��ng)�P��ˬ��......

4360��ȫ�g�[��-�g�[��-360��ȫ�g�[�����d ......

5�ȸ�g�[�� XP��-�ȸ�g�[�� XP��-�ȸ�g�[......

6Kittenblock�ؑc�������ð�-�C���˾���......

7seo�������(�������) -SEO��會�(y��u)������......

8Notepad3-ӛ�±�ܛ��-Notepad3��......